# Design and Generation of High-Performance Transceivers

7. 4. 2025

Jaeduk Han

Nifty Chips Laboratory @ HYU niftylab.github.io

## Motivation

Bandwidth Scale-Up: In the AI era, high-performance transceivers are essential to handle massive data, requiring over 100 Gb/s per channel

<sup>[</sup>NVIDIA, Synopsys]

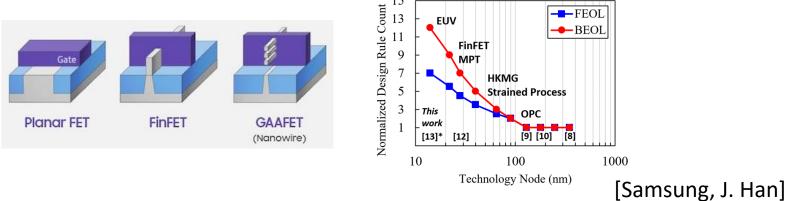

• **Design Complexity:** Designing and fabricating these circuits in nanometer technologies require significant time and effort

Nifty Chips Lab @ HYU

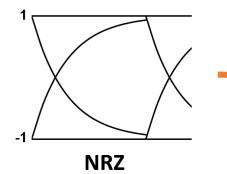

• Increase the number of transmitted bits per symbol

PAM-4

5/7 3/7 1/7 -1/7 -3/7 -5/7 -1 PAM-8

**PAM Signal Evolutions**

**Confidential Materials - Do Not Distribute**

High-Bandwidth Solution: PAM-X Reception

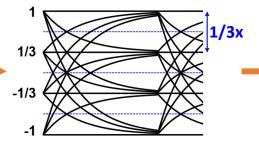

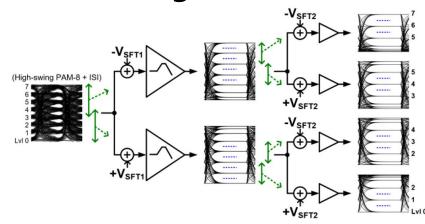

A multi-path receive chain ensures high-fidelity recovery of PAM-8 signals, demonstrating the highest PAM-8 mixed-signal data rate ever reported

### **Receiver Architecture**

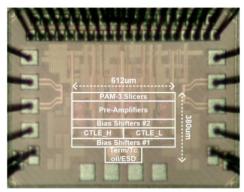

**Chip Micrograph**

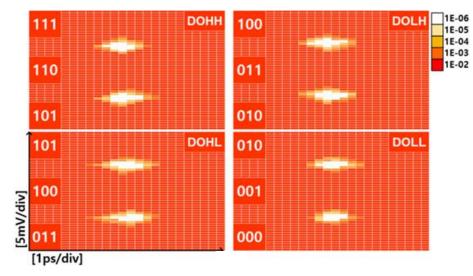

#### Measured Eye Diagrams at 103Gb/s

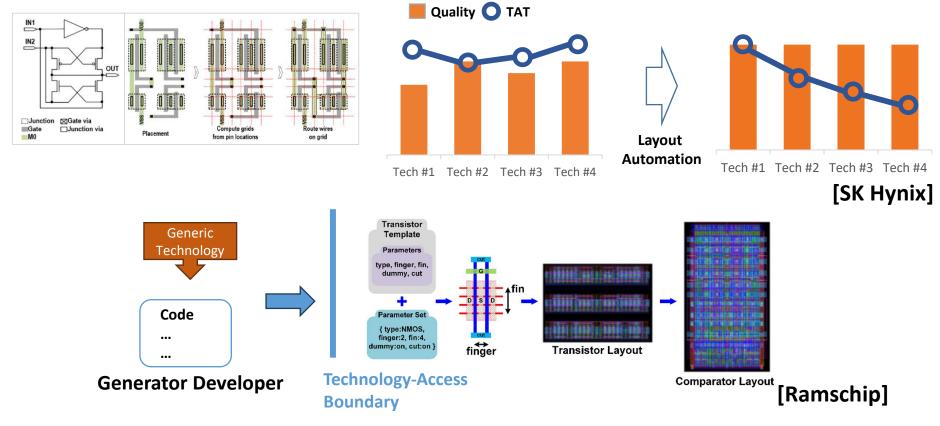

High Productivity Solution: Design Automation (1)

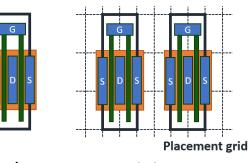

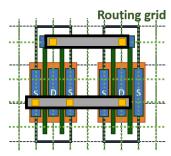

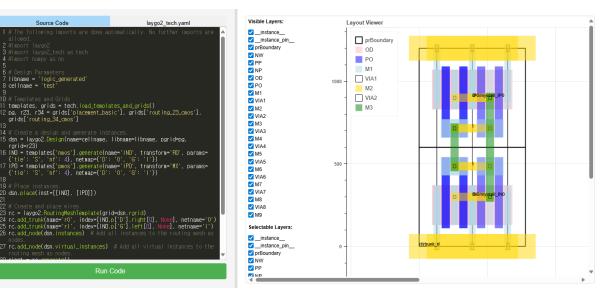

Our framework, LAYGO, automates layout generation using templates and grids

Templates

On-grid placement

#### On-grid routing

A temporary website is open, please try! - http://laygo.hanyang.ac.kr

High Productivity Solution: Design Automation (2)

- Applied to sub-7nm FinFET, DRAM, and CIS, over 5x productivity improvement is proven

- We're now integrating AI and LLMs—stay tuned!

A temporary website is open, please try! - http://laygo.hanyang.ac.kr

Nifty Chips Lab @ HYU